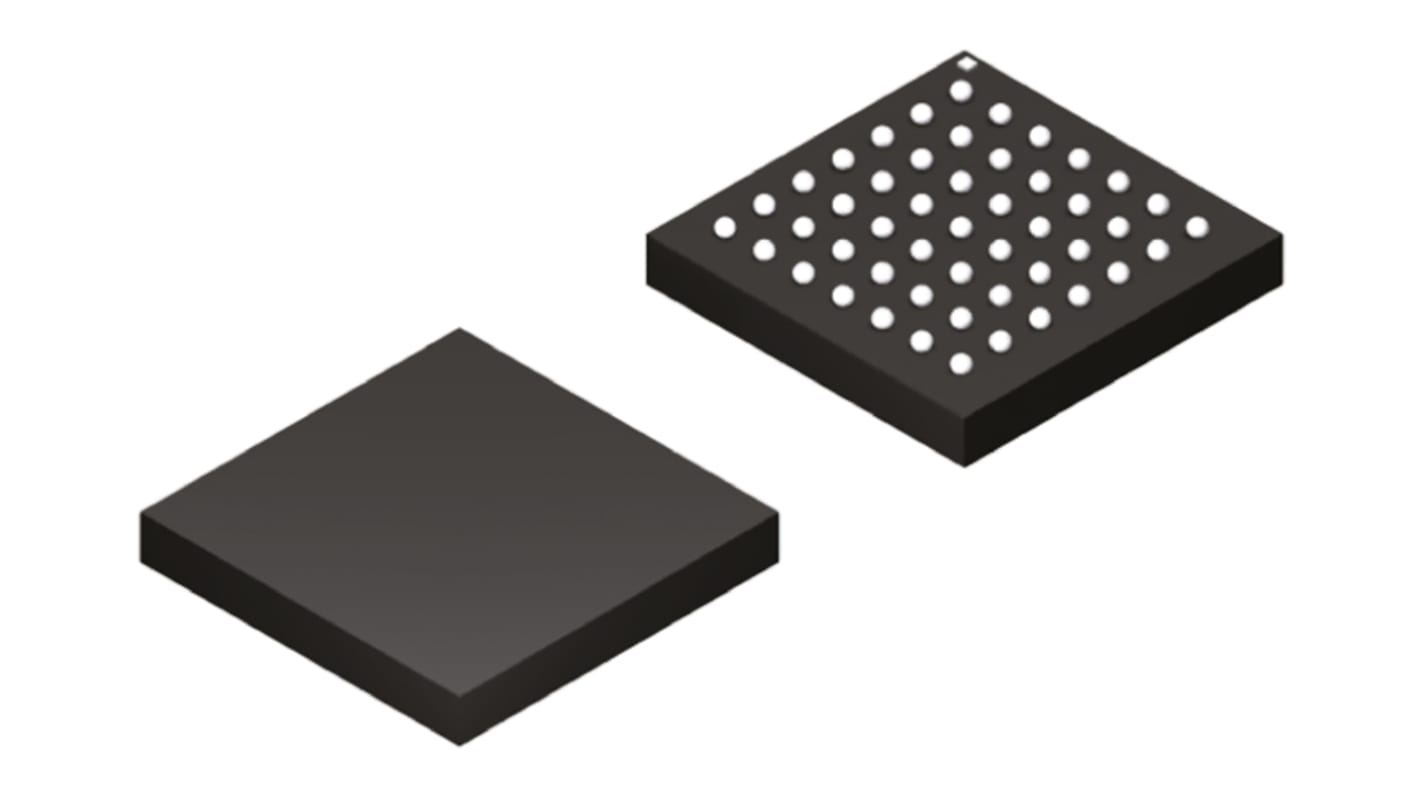

Lattice Semiconductor FPGA iCE40 LP/HX 1280 celdas, 64 kB 160 bloques, 49 pines UCBGA

- Código RS:

- 168-4224

- Referência do fabricante:

- ICE40LP1K-CM49

- Fabricante:

- Lattice Semiconductor

A imagem representada pode não ser a do produto

Subtotal (1 bandeja de 490 unidades)*

1 913,94 €

Informações de stock atualmente inacessíveis - Verifique novamente mais tarde

Unidad(es) | Por unidade | Por Bandeja* |

|---|---|---|

| 490 + | 3,906 € | 1 913,94 € |

*preço indicativo

- Código RS:

- 168-4224

- Referência do fabricante:

- ICE40LP1K-CM49

- Fabricante:

- Lattice Semiconductor

Especificações

Documentação Técnica

Legislação e Conformidade

Detalhes do produto

Seleciona um o mais atributos para encontrar produtos semelhantes.

Selecionar tudo | Atributo | Valor |

|---|---|---|

| Marca | Lattice Semiconductor | |

| Tipo de producto | FPGA | |

| Serie | iCE40 LP/HX | |

| Número de células lógicas | 1280 | |

| Número de unidades lógicas | 160 | |

| Número de registros | 1280 | |

| Tipo de montaje | Superficie | |

| Tensión de alimentación mínima | 1.14V | |

| Encapsulado | UCBGA | |

| Tensión de alimentación máxima | 1.26V | |

| Número de pines | 49 | |

| Número de bits de RAM | 64kB | |

| Temperatura de Funcionamiento Mínima | -40°C | |

| Temperatura de funcionamiento máxima | 85°C | |

| Longitud | 3mm | |

| Altura | 0.9mm | |

| Certificaciones y estándares | Halogen Free | |

| Estándar de automoción | No | |

| Selecionar tudo | ||

|---|---|---|

Marca Lattice Semiconductor | ||

Tipo de producto FPGA | ||

Serie iCE40 LP/HX | ||

Número de células lógicas 1280 | ||

Número de unidades lógicas 160 | ||

Número de registros 1280 | ||

Tipo de montaje Superficie | ||

Tensión de alimentación mínima 1.14V | ||

Encapsulado UCBGA | ||

Tensión de alimentación máxima 1.26V | ||

Número de pines 49 | ||

Número de bits de RAM 64kB | ||

Temperatura de Funcionamiento Mínima -40°C | ||

Temperatura de funcionamiento máxima 85°C | ||

Longitud 3mm | ||

Altura 0.9mm | ||

Certificaciones y estándares Halogen Free | ||

Estándar de automoción No | ||

- COO (País de Origem):

- KR

Matrices De Puerta Programables En Campo Lattice Semiconductor

Un FPGA es un dispositivo semiconductor compuesto de una matriz de bloques lógicos configurables (CLB) conectados mediante interconexiones programables. El usuario determina estas interconexiones mediante programación SRAM. Un CLB puede ser simple (puertas Y, O, etc) o complejo (un bloque de RAM). FPGA permite realizar cambios en un diseño incluso después de haber soldado el dispositivo en un PCB.

Links relacionados

- Lattice Semiconductor FPGA iCE40LP1K-CM49 iCE40 LP/HX 1280 celdas, 64 kB 160 bloques, 49 pines UCBGA

- Lattice Semiconductor FPGA iCE40 1280 celdas, 64000 bit 160 bloques, 100 pines VQFP

- Lattice Semiconductor FPGA iCE40HX1K-VQ100 iCE40 1280 celdas, 64000 bit 160 bloques, 100 pines VQFP

- Lattice Semiconductor FPGA iCE40 3520 celdas, 80000 bit 440 bloques, 144 pines TQFP

- Lattice Semiconductor FPGA iCE40HX4K-TQ144 iCE40 3520 celdas, 80000 bit 440 bloques, 144 pines TQFP

- Transformador de corriente LEM HX 10 A 15V

- Transformador de corriente LEM HX 20 A 15V

- Barra de bus Legrand, 4 049 38, 2 Fases, 400 V 35.5 mm HX HX